7400 Quad 2-Input NAND

7410 Triple 3-Input NAND

7490 Decade Counter

7492 Divide-by-12 Counter

74123 Dual Retriggerable Single Shot

NOTE

1. 출력 Pulse 폭을 조절하기 위한 외부 Timing Capacitor는 Cext와 Rext/Cext 사이에 연결

2. Pulse 폭을 정밀하게 조정하려면 외부 저항을 Rext/Cext와 Vcc 사이에 연결

3. Pulse 폭을 가변형으로 하려면 외부 가변저항을 Rint/Cext와 Vcc 사이에 연결.

1) Cext > 1000pF 일때의 출력 Pulse 폭 Tw은 Vcc=VRC=5V일 때 다음과 같이 결정된다.

Tw = KRextCext (1+0.7/Rx)

여기서 Rext는 ㏀ 단위, Cext는 pF 단위, Tw는 nano-second 단위, K ≒ 0.45

2) Cext ≤ 1000 pF 일 때는 대략 다음과 같다.

Tw = 6+0.05Cext (pF) + 0.45Rext(㏀)Cext + 11.6Rext

7447 BCD-to-decimal decoder/driver

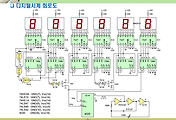

4-digit digital 시계의 구성도와 회로

1. Crystal Oscillator

Digital 시계 회로에서 사용될 수정 결정을 이용한 Crystal Oscillator는 TTL을 이용한 무안정 Multivibrator이다. Inverter의 입출력 사이를 적당한 값의 저항으로 접속하면 반전 증폭 회로와 거의 같은 작용을 한다. 2개의 Inverter에 Condensor로 연결하여 조합을 만들면 구형파의 발진을 계속할 수 있는데, 여기서 수정 결정편을 사용하면 수정의 고유 발진 주파수에 의해 온도변호나 R 또는 C값 변화의 영향을 거의 받지 않고 안정된 구형파 출력을 얻을 수 있다.

2. 분주회로

분주 회로에서 나오는 신호를 시계에서 사용할 1Hz 신호로 만들기 위해 주파수 분할을 한다. 주파수 분할은 두가지 종류로 나눌 수 있는데, 우선 Divide-by-10과 Divide-by-6 분할회로를 만들어야 한다. 이를 위해 Decade Counter (7490)와 Divide-by-12 Counter(7492)를 이용한다. (7490만을 이용할 수도 있다.)

1) Divide-by-10 회로

※ 모든 7490은 동일 방법으로 연결하지만 reset이 필요한 곳에서는 2번과 3번 단자를 reset 신호가 나오는 곳과 연결한다.

※ 분 Counter의 7490은 다른 연결방법은 동일하나 출력 단자인 Qa, Qb, Qc, Qd는 7447의 해당단자로 연결한다. (Qa→A, Qb→B, Qc→C, Qd→D)

2) Divide-by-6 회로

7492는 기본적으로 2진+6진 Counter (12진)로서 Qc 출력까지만 이용하면 6진 Counter로 사용된다.

※ Reset이 필요한 경우에는 6번 7번 단자를 Reset 신호가 나오는 곳에 연결한다.

※ 7490을 이용하여 6진 Counter를 만드는 방법을 사용할 수도 있다. 이때 7490의 출력이 0101(510)을 계수한 다음 0110(610)으로 되는 순간 Qb와 Qc가 동시에 상태 1이 되므로 계수기를 0000으로 Reset시키는 방법을 쓴다.

3. 조정회로

표시장치에 임의로 나타나는 시계를 맞추기 위해서 필요한 조정회로는 3단 입력 NAND gate를 이용한다. 조정용 스위치 S와 F가 열려있는 상태에서는 1/60Hz의 신호에 의해 출력신호가 결정되고 스위치 S가 닫힌 경우 1Hz 신호에 의해서 스위치 F가 닫힌 경우에는 10Hz 신호에 의해 출력신호가 결정되게 된다. 즉 정상적인 경우의 1분 신호가 1초에 한번 또는 1/10초에 한번씩 나와서 시계를 빨리 가도록 할 수 있게 된다. 동시에 스위치 S와 F 둘 중의 하나가 닫힌 경우에는 조정회로 바로 저느이 7490과 7492의 출력이 0으로 Reset시키는 신호를 발생시킨다.

4. 시 Counter회로

시간을 표시하기 위해서는 약간의 조작이 필요하다. 시간 10자리수는 0과 1만 나타나게해야하고 1자리수의 경우는 Counter 순서가 (1-2-3-4-5-6-7-8-9-0-1-2)-(1-2-3-.....)의 순서로 Counter되도록 해야한다.

이를 위해 13이 Counter되는 순간에 7490(A)와 7490(B)를 Reset시킴과 동시에 74123에서 한개의 Pulse를 발생시켜 01이 되도록 만들도록 한다. 13이 되는 순간은 7490(B)의 Qa 출력이 1이고, 7490(A)의 Qa와 Qb가 1이 되는 순간이므로 이들을 AND gate의 입력으로 넣어 이들이 동시에 1인 순간(13) 7490(A)와 7490(B)를 Reset시킨다. 그리고 이 ANd gate의 출력 논리 1은 74123으로 하여금 Pulse 하나를 발생시키도록 하여 OR gate를 거쳐 7490(A) Qa 출력이 1이 되도록 한다.

5. BCD-to-decimal decoder/driver

7490과 7492의 BCD 출력을 7447의 입력으로 넣어 LED Display를 구동하는 IC chip으로 7447을 사용한다. BCD code를 해석하여 10진수 표현으로 나타내기 위한 것으로서 출력선은 330Ω 저항을 통해 LED의 해당 단자에 연결한다.

※ 시 Counter의 7490(B)와는 Qa 입력단자만 연결하고 나머지는 접지시킨다. 출력도 b와 c만 LED에 연결하고 시간이 1-9시까지 표시될 때는 LED가 모두 꺼지게 하기 위해 3번 단자만 +5V에 연결 4번은 연결하지 않으며 5번은 접지시킨다.

※ 분 Counter의 10자리는 Qd입력단자를 접지시킨다.

'전자 > 디지털클락' 카테고리의 다른 글

| [디지털 클락] LM7805(전원 레귤레이터) (0) | 2021.11.28 |

|---|---|

| [발진회로] CSS555 / CSS555C TIMER (0) | 2020.07.28 |

| [디지털클락] 디지털클락 회로 (12시 분주기 캐패시터) (0) | 2020.07.08 |

| [디지털 클락] 4020 데이터시트 (0) | 2020.07.08 |

| [디지털 클락] 디지털클락 회로 (오전 오후 12시 분주기 크리스탈) (0) | 2020.07.08 |

댓글